Método PLL e princípios de síntese de sinais de alta frequência. Características dinâmicas do PLL

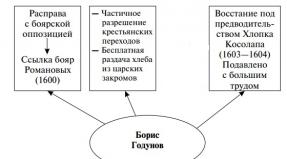

O sistema de controle automático de frequência de fase, doravante denominado PLL (abreviatura estrangeira Phase - Locked Loop, PLL), é uma unidade independente que faz parte de diversos equipamentos de comunicação, sistemas de transmissão via satélite e transmissão de dados, bem como dispositivos que são fontes estáveis de sinais.

O primeiro sistema PLL foi desenvolvido em 1930 pelo engenheiro francês Bellize. No entanto, tornou-se amplamente utilizado em 1960 com o advento dos primeiros componentes PLL integrados. Tem havido um preconceito tradicional contra o PLL, em parte devido à dificuldade de implementá-lo em componentes discretos, e em parte devido a dúvidas sobre a confiabilidade de sua operação. Com o tempo, quando começaram a aparecer componentes altamente integrados, implementando em um chip quase todos os nós PLL necessários (com exceção de alguns elementos externos), este sistema, com design adequado e correto, tornou-se um nó bastante confiável e digno de nota.

O sistema PLL pode ser pensado como um sistema de realimentação negativa contendo um ganho direto G(s) e um ganho de realimentação H(s), bem como um valor e(s) que caracteriza o sinal de diferença entre o sinal de entrada Vi e o circuito sinal opinião V 0 .

A função de transferência da malha fechada do circuito OOS (Fig. 1) terá a forma:

onde, G CL - coeficiente de transmissão em malha fechada (de Ganho Malha Fechada).

Onde - número complexo, caracterizando o vetor circular, e é a frequência circular.

O detector de fase PD (Phase Detector) compara dois sinais de frequência e gera um sinal de saída proporcional à diferença de fase. Este sinal de diferença é um sinal de erro que caracteriza a estabilidade do sistema, e no estado estacionário seu valor tende a zero. Em outras palavras, o sistema é estável quando o valor de e(s) é zero. Por isso, este sistema, e consequentemente o sistema PLL, é um sistema de controle automático ou sistema de rastreamento, e a medida do controle de frequência é a diferença de fase entre o sinal de entrada (referência) e o sinal do circuito de feedback.

Vamos agora considerar o modelo PLL básico padrão (Fig. 2) e seus componentes:

- detector de fase PD e fonte de corrente CP (Bomba de Carga);

- filtro de loop ou filtro passa-baixa com função de transferência Z(s);

- oscilador controlado por tensão VCO (Oscilador Controlado por Tensão);

- divisor no circuito de feedback com fator de divisão N.

Em um detector de fase, conforme mencionado acima, dois sinais de frequência são comparados e é gerado um sinal de saída que é proporcional à sua diferença de fase. Quando ambos os sinais são iguais em fase e frequência, o sinal de erro será zero e o circuito será “fechado”.

A seguinte equação pode ser dada para caracterizar o valor do sinal de erro e(s):

quando e(s) = 0,

segue daqui

Quando F 0 N·F ref , um sinal periódico diferencial é gerado na saída do detector de fase, que é então alimentado da saída da fonte de corrente para um filtro passa-baixa.

Este sinal de erro de fase amplificado e filtrado na forma de uma tensão de controle, por sua vez, acionará o VCO cuja frequência será aumentada ou diminuída conforme necessário por um valor de K v V, onde K v é a sensibilidade do VCO em MHz/V e V é a mudança na tensão na entrada do VCO. Isso continuará até que o valor de e(s) se torne zero e o circuito seja bloqueado. Portanto, o VCO converte a tensão de entrada que recebe em sua derivada temporal da fase, ou seja, frequência. Assim, a fonte de corrente e o gerador controlado por tensão servem como integrador, que, ao detectar um sinal de erro, ajusta o valor da frequência de saída para que o valor deste erro seja reduzido a zero. Devido à integração, aparece uma mudança de fase de 90º na malha de controle. Assim, o integrador incluído no circuito OOS introduz um atraso de fase adicional de 90º e em frequências onde o ganho é igual à unidade pode causar autoexcitação. Uma solução é não incluir componentes na malha de controle que introduzam atraso de fase adicional, pelo menos em frequências onde o ganho é próximo da unidade.

Para esclarecer um pouco a situação, vamos voltar um pouco. A frequência do VCO pode ser controlada aplicando uma tensão apropriada à sua entrada. Aqui, ao que parece, você pode fazer o mesmo que em qualquer amplificador de feedback - introduzir um circuito de controle com um determinado coeficiente de transmissão, como é feito ao projetar circuitos usando amplificadores operacionais. Mas há uma diferença importante: nos circuitos baseados em amplificadores operacionais, o valor controlado pela realimentação coincidia com o valor medido para gerar o sinal de erro, ou pelo menos era proporcional a ele. Por exemplo, amplificadores de tensão medem a tensão de saída e ajustam a tensão de entrada de acordo. A situação é um pouco diferente para o sistema PLL, pois aqui medimos a fase e ajustamos a frequência, ou seja, como mencionado acima, ocorre a integração, a partir da qual surge o mesmo deslocamento de fase. No entanto, deve-se notar que os amplificadores operacionais têm um atraso de fase de 90º em quase toda a sua faixa de frequência, mas ainda funcionam bem.

Para não incluir no circuito elementos que introduzam atraso de fase adicional, podemos propor e analisar uma das opções para a construção de uma malha de controle, o chamado “circuito de primeira ordem”, no qual um amplificador operacional atua como uma corrente fonte, mas um filtro passa-baixa é excluído do circuito. Com este desenho do circuito, a entrada do VCO é conectada diretamente à saída da fonte de corrente do amplificador operacional, o que não permite suavizar ruídos e flutuações do sinal de entrada, já que este circuito não possui o chamado “ propriedade flywheel”, que é garantida pela introdução de filtragem passa-baixa. Além disso, o "loop de primeira ordem" não mantém uma relação de fase constante entre o sinal de referência e o sinal VCO pela mesma razão que a saída da fonte de corrente está diretamente conectada à entrada do VCO. De tudo o que foi dito acima, pode-se supor que “loops de primeira ordem” não são adequados para construir loops de controle PLL.

A próxima abordagem é usar um "loop de segunda ordem" que introduz filtragem passa-baixa adicional. Tal circuito possui a necessária propriedade de “volante”, suavizando interferências e flutuações do sinal de entrada, além disso, reduz a banda de captura, ao entrar na qual a frequência do VCO começa a se estabilizar pelo sistema PLL; Existe também uma banda de retenção, ou seja, a banda de dessintonização máxima do VCO, na qual o PLL de malha fechada estabiliza a frequência do VCO. A largura das bandas de captura e retenção depende precisamente do tipo de resposta de fase de frequência do filtro passa-baixa e do coeficiente geral de transmissão da malha de controle. Em um sistema PLL adequadamente projetado, a banda de retenção é maior ou igual à banda de captura, o sistema é estável e não se autoexcita. Deve-se notar também aqui que com a introdução da filtragem de baixa frequência, o tempo de aquisição também aumenta ligeiramente, o que caracteriza a velocidade de entrada na aquisição e manutenção do sistema PLL no modo de rastreamento durante uma mudança brusca de frequência. Analisando o exposto, podemos concluir que “circuitos de segunda ordem” são adequados para o sistema PLL, que proporcionam pequenas flutuações na fase do sinal de saída, e também possuem algumas propriedades de memória ou “volante”.

A função de transferência geral para o PLL pode ser representada usando a expressão G CL para o sistema de realimentação negativa:

Aqui introduzimos o conceito adicional de Forward Gain, denotado por G, como um coeficiente que caracteriza o ganho na direção direta, e o conceito de Loop Gain, denotado por GH, como o coeficiente de transmissão do loop.

Quando o valor de GH é maior que um, podemos dizer que a malha está fechada, e a função de transferência para o sistema PLL com fator de divisão N tem a forma:

Na Fig. A Figura 3 mostra a dependência da frequência de saída do VCO na mudança na tensão de entrada.

Antes de começarmos a considerar métodos para sintetizar sinais, é aconselhável considerar um modelo um tanto abstrato (Fig. 4) que mostra o processo de formação de uma sequência de um fluxo de dados inteiro.

Na Fig. 4 estão marcados:

No lançamento inicial do sistema, ou seja, quando i = 1 e n = 0, P 0 terá algum valor fixo, que, “passando” pelos divisores M e N, nos dará o valor 1. Na primeira etapa, nada foi adicionado ao valor do divisor N, pois para i = 1 n = 0. Na segunda etapa, para i = 2 e n = 1, aumentamos o valor do divisor N em n e breve. Uma condição indispensável é um valor constante em todas as etapas do ciclo. Parece que tudo é simples e claro, mas analisando todo o processo podemos derivar as seguintes expressões, que podem ser úteis na análise do funcionamento de sintetizadores reais.

(laboratório 2, layout com integrador eletrônico)

Objetivo do trabalho:

1) familiarização com os elementos funcionais do sistema PLL e o princípio de seu funcionamento;

2) estudo da precisão em função da estrutura e parâmetros do sistema;

3) estudo das possibilidades de alteração das propriedades dinâmicas do sistema utilizando o método de correção sequencial.

Descrição da configuração do laboratório

A configuração do laboratório consiste em um protótipo de sistema PLL, um gerador de sinais harmônicos e um osciloscópio. O sistema PLL em sua configuração mais simples contém um discriminador de fase (converte a diferença de fase de dois sinais em uma tensão de controle), circuitos de correção e um gerador controlado (um elemento reativo controlado por tensão está incluído no circuito de acionamento deste gerador). Se os sinais de entrada e saída do sistema PLL estiverem fora de fase (ou frequência), então o discriminador de fase produz uma tensão de controle do sinal correspondente, sob a influência da qual os parâmetros do circuito de temporização do gerador controlado mudam e, consequentemente, a frequência (e fase) do sinal de saída muda de modo a reduzir o distúrbio inicial. Sem levar em conta a não linearidade das características estáticas dos elementos funcionais e a inércia do discriminador de fase, a função de transmissão do sistema PLL no estado aberto pode ser representada como:

onde está a função de transferência do circuito de correção; – fator de ganho.

Em um sistema de controle automático de astatismo de 1ª ordem, o erro de rastreamento dinâmico depende da taxa de variação da influência (no nosso caso, a fase) e do ganho do sistema:

(1)

(1)

onde é o erro de rastreamento de fase residual em graus (é útil considerar a fase como um valor dimensional); – dessintonização inicial da frequência dos geradores [Hz].

Existem 3 opções para ligar o sistema PLL mais simples (switch S1):

Sem correção (=1);

;

;

Com correção sequencial do formulário:  ,

,

Além disso, as constantes de tempo dos circuitos de correção T 1, T 2 e T 3 dependem dos valores dos resistores e capacitâncias indicados no layout.

As relações de frequência e fase dos sinais dos geradores controlados e externos são observadas usando figuras de Lissajous na tela do osciloscópio. Para medir o erro de rastreamento, é utilizado um deslocador de fase, conectado na saída do oscilador controlado. Primeiro coloque o botão “Detuning” do oscilador externo na posição “0” e no estado aberto do sistema PLL (posição 1 da chave S1) faça um ajuste aproximado manual da frequência do oscilador externo de acordo com o resultado final ( Figura de Lissajous - elipse). Em seguida, o anel de rastreamento é fechado e, com a ajuda de um deslocador de fase, a figura de Lissajous é convertida em uma forma conveniente para observação (uma linha ou “oito”). Posteriormente, a frequência do gerador externo é alterada usando o botão “Detuning”. Uma mudança suave na frequência do sinal de entrada afeta o erro de rastreamento, o que leva à deformação da figura de Lissajous. Ao retornar a figura à sua posição anterior usando um deslocador de fase, você pode medir (na escala do deslocador de fase) a quantidade de erro residual.

Deve-se ter em mente que a dependência real, devido à não linearidade da característica estática (discriminatória) do discriminador de fase, é descrita por uma função ímpar não linear. Neste caso, é possível obter experimentalmente apenas um fragmento da dependência, sobre o qual deverá ser identificada uma seção linear para o cálculo do coeficiente.

Para uma avaliação qualitativa da velocidade e grau de oscilação dos processos transitórios no sistema PLL, é fornecido um circuito de mudança de fase no circuito do sinal de entrada, ligado pela chave seletora “Phase Jump”.

Um sistema PLL totalmente equipado contém adicionalmente um integrador eletrônico: um “equivalente de motor” é conectado.

Atribuição de trabalho

1. Ligue o gerador, a placa de ensaio e o osciloscópio.

2. Abra o sistema PLL (interruptor na posição 1).

3. Configure um osciloscópio para observar as figuras de Lissajous.

4. Ao alterar a frequência do oscilador, certifique-se de que as frequências do oscilador externo e do oscilador controlado do sistema PLL coincidem (uma elipse na tela do osciloscópio). Feche o sistema PLL (interruptor na posição 2). Meça a banda de retenção do sistema PLL.

5. Coloque o botão “frequência do gerador” na posição intermediária (ver parágrafo 4). Usando um deslocador de fase, fixe a posição da elipse, imaginando-a como uma linha ou um oito. Alterando a frequência do gerador (o botão de “desafinação”) e medindo o incremento na mudança de fase usando um deslocador de fase, construa uma relação (você deve obter uma função ímpar). Para construir um gráfico, são necessários 3-5 pontos quando a frequência é desafinada em uma direção e o mesmo número de pontos na outra.

6. Para a seção linear da dependência, determine o ganho usando a fórmula (1). Este valor deverá ser acordado com o professor.

7. Usando o valor obtido, construa características logarítmicas assintóticas para 3 opções para ligar o sistema PLL de primeira ordem de astatismo (construa todos os LCHs em um gráfico para facilitar a comparação; os parâmetros dos elementos de correção são indicados no layout) . Usando características logarítmicas, avalie a qualidade dos processos transitórios.

8. Avalie qualitativamente os processos transitórios no sistema PLL (para isso, é utilizada a chave seletora “salto de fase”).

9. Ligue o “motor equivalente” e repita os passos 4 a 6 (ao alterar a frequência do gerador, leve em consideração a recarga de longo prazo da capacidade do integrador eletrônico). Desenhe o circuito do integrador eletrônico e calcule sua função de transferência (de forma geral).

1. Diagrama funcional Sistemas PLL, circuitos de elementos corretores indicando os valores de resistores e capacitâncias, circuito de integrador eletrônico, funções de transferência de sistema em malha aberta para todas as opções em estudo.

2. Tabela e gráfico de dependência, cálculo e constantes de tempo dos elementos corretivos.

3. LC assintótico para 3 opções para construção de um sistema PLL de astatismo de primeira ordem.

4. Características comparativas processos de transição e sua explicação.

5. Bandas de retenção dos sistemas PLL estudados.

6. Estrutura do filtro modelador para a situação Δf=const.

1. Como funcionam os elementos funcionais do sistema PLL e de todo o sistema?

2. Qual parâmetro do sinal de entrada é informativo para o sistema PLL?

3. Qual é a forma da estrutura do filtro modelador no caso de Δf(t)=0, Δf(t)=const, Δf(t)=vt? Qual é a estrutura do ACS acordado?

4. Como as propriedades do sistema PLL mudam com o aumento (diminuição) do ganho?

5. Com que finalidade são incluídos elementos corretivos no sistema PLL de primeira ordem do astatismo?

6. Como as propriedades do sistema PLL mudam com um integrador eletrônico?

O sistema PLL (phase-locked loop system), como o próprio nome sugere, é um sistema de controle automático (sistema escravo), cuja frequência de sintonia é determinada pela frequência do sinal de controle, e o sinal de incompatibilidade é a diferença de fase entre o sinal de controle e o sinal de feedback. Devido ao fato de a sintonia ser realizada por diferença de fase, o sistema é asstático em relação à frequência: em estado estacionário, a frequência de sintonia é exatamente igual à frequência do sinal de controle. Sob certas condições, o sistema PLL pode ficar asstático e fora de fase.

Junto com a propriedade básica de autoajuste, o sistema PLL possui a propriedade de filtrar e se comporta, independente da finalidade funcional, como um filtro polinomial de rastreamento. O sistema PLL é um sistema com capacidades multifuncionais e é usado para modulação e demodulação de frequência, filtragem de frequência (incluindo filtragem da função de modulação de frequência), multiplicação e conversão de frequência, extração de vibração de referência para detecção coerente, etc.

O sistema PLL pode ser analógico, pulsado, digital ou combinado (analógico-pulso, pulso-digital e assim por diante). Em um sistema PLL analógico, existe um sinal contínuo caracterizado por valores de parâmetros instantâneos em cada momento. Em um sistema de pulso, os parâmetros do sinal são caracterizados por valores discretos, que podem ser instantâneos ou intervalares. Um sinal de pulso com amostras instantâneas é, por exemplo, um sinal retangular (“tipo meandro”) de um gerador controlado, caracterizado por valores de frequência instantâneos em pontos de mudança de nível. Um sinal de pulso com leituras de intervalo é, por exemplo, um sinal de um detector de fase pulsada (PD), cuja duração dos pulsos é determinada pelo intervalo de fase medido. Um sinal de pulso de intervalo pode causar temporização e outros tipos de distorção. Um sistema PLL digital utiliza, portanto, um sinal digital, que é um fluxo discreto de dados determinado pelos valores de amostras quantizadas do sinal analógico e expresso em um código digital. Amostras quantizadas de um sinal digital também podem ser instantâneas ou intervalares.

Abaixo está uma análise geral de engenharia de um sistema PLL com elementos analógicos e de pulso e discute as aplicações do sistema.

Os sistemas PLL em consideração são amplamente utilizados em componentes microeletrônicos produzidos por empresas renomadas. Por exemplo, Analog Devices usa um sistema PLL:

- em sintetizadores de um e dois canais ADF410x/1x/5x e ADF420x/1x/5x tipos “Integer-N” e “Fractional-N” com frequências programáveis (sintonizáveis) de até 3,7 GHz;

- para multiplicação da frequência de clock nos DACs da série TxDAC+ AD9751/3/5 (300 MHz), AD9772/4 (400/128 MHz), em sintetizadores-moduladores digitais (DDS) AD9852/4 (300 MHz) e moduladores AD9853/6 (168/200MHz);

- multiplicar a frequência por k = 2 N /n vezes, onde n é um número inteiro da série 1, 2, ... 2 N /2,5, - com sintetizadores DDS AD9850/1/2/4 como divisores de frequência em circuitos de realimentação (por exemplo, em N = 48 e uma frequência máxima após multiplicação de 300 MHz ao usar o AD9852);

- como modulador de frequência combinado com um sintetizador de frequência e um demodulador de frequência combinado com um conversor de frequência - no chip transceptor AD6411 do sistema DECT;

- como modulador de quadratura combinado com conversor de frequência de quadratura - no chip transceptor AD6523, utilizado em conjunto com o sintetizador AD6524 (também baseado em PLL), - em sistemas GSM e DCS;

- como fonte de frequência de referência com saída em quadratura para o demodulador no chip transceptor GSM AD6432.

A Texas Instruments usa o sistema:

- em sintetizadores de frequência de dois e três canais TRF2020 - até 0,25, 0,25 e 1,2 GHz, TRF2050 - até 0,25 e 1,2 GHz, TRF2052 - até 0,15 e 2,0 MHz e TRF3040, que também é um modulador - até 0,2 e 2,0 GHz;

- para sintetizar sinais de frequência de referência para moduladores em microcircuitos TRF3040 e TRF3520;

- para multiplicação de clock nos processadores de sinais digitais TMS320C54x, TMS320C62x, TMS320C67x e TMS320VC33.

A Motorola (setor de produtos de semicondutores) utiliza o sistema em sintetizadores de frequência de dois canais MC145181 (até 550 e 60 MHz), MC145225 (até 1,2 e 0,55 GHz), MC145230 (até 2,2 e 0,55 GHz), etc., destinados a equipamentos de comunicação de rádio de vários sistemas.

Gran-Jansen AS (Noruega) utiliza um sistema PLL no transceptor GJRF400 (GJRF10), operando na faixa de frequência de 300–500 MHz, para síntese de onda de referência e para modulação de frequência analógica.

A lista acima está longe de estar completa, porém, os microcircuitos listados caracterizam de forma bastante completa as possibilidades de utilização do sistema PLL.

Relacionamentos básicos

Em termos gerais, qualquer sistema de controle automático, independente de sua finalidade, contém um dispositivo de medição com um subtrator na entrada e um objeto de controle, cuja saída está conectada ao subtrator. No subtrator, o valor de controle e o valor controlado (da saída do objeto controlado), que é o valor de feedback, são comparados. Junto com os conceitos de controle e grandezas controladas, utilizaremos os conceitos de entrada e saída, que determinam a finalidade funcional do sistema. Em geral, as grandezas de entrada e saída nem sempre são controladas e controladas (no sentido especificado destes termos). Função de transferência do sistema -

K(p) = x saída /x entrada = K pr (p)/, (1)

onde x out e x in são quantidades de saída e entrada, e K pr (p) e K arr (p) são as funções de transferência de circuitos de transmissão direta (de entrada para saída) e feedback negativo (de saída para entrada), p é o operador Laplace (o sinal de mais no denominador significa que o feedback é negativo). A quantidade de entrada pode ser fornecida à entrada de qualquer elemento, e a quantidade de saída também pode ser obtida da saída de qualquer elemento do sistema.

Arroz. 1

Na Fig. A Figura 1a mostra um diagrama do sistema PLL mais simples contendo um detector de fase PD (dispositivo de medição), filtro F e um gerador controlado UG (objeto de controle). FD e UG são elementos obrigatórios do sistema, e um filtro que afeta suas propriedades dinâmicas (frequência) pode estar ausente. A variável de controle é a frequência w 0 + D w entrada da tensão alternada na entrada PD, cujos componentes são: w 0 - a frequência de referência do sistema e D w entrada - a mudança na frequência, que é a entrada valor que afeta o sistema. O valor de feedback é a frequência do oscilador, igual a w 0 + D w arr, onde D w arr = D w entrada – pD j, e pD j e D j são mudanças na frequência e fase na entrada PD causadas por Entrada Dw. Na Fig. A Figura 1b mostra um diagrama de uma variante do sistema, que difere porque apenas a frequência de referência w 0 atua na entrada do PD, e o valor de entrada do sistema é a tensão uin na entrada do CG, aplicada através do “ +” somador. Grandezas de entrada e saída D w in e u out na Fig. 1a determine a finalidade do sistema - um demodulador de frequência, e u in e w 0 + D w out na Fig. 1b - modulador de frequência. Funcionalmente, o somador da Fig. 1b é um subtrator, uma vez que a realimentação negativa opera na malha do sistema.

Apesar de a variável de controle no sistema PLL ser a frequência, no PD não são as frequências que são comparadas, mas sim as fases das tensões em sua entrada. Como resultado, a diferença de fase, que é a integral da diferença de frequência, é igual a D j = (D w in - D w arr)/p (Fig. 1a) ou D j = -D w out /p ( Fig. 1b), e a função de transferência PD, respectivamente, K PD (p) = K PD /p, onde K PD é o coeficiente de transmissão com dimensão V/rad. A diferença de fase na entrada PD, além de D j, pode conter uma componente constante inicial j 0, na qual na entrada PD j = j 0 + D j. A componente j 0 é a constante de integração e é determinada pela escolha do modo do sistema PLL levando em consideração a característica do detector do PD.

Função de transferência do sistema PLL de acordo com o circuito da Fig. 1a, utilizado para demodulação de frequência, é caracterizado pela expressão

K BH (p) = U fora / D w dentro = K 0 /, (2)

onde u out é a tensão na saída do filtro (tensão de saída do demodulador), devido à mudança de frequência na entrada D w in, K 0 = 1/K UG é o coeficiente de transmissão do sistema (neste caso, no frequência “zero”), t 0 = 1 /K FD K F K UG é a constante de tempo “própria” (sem levar em conta o filtro k F (p)) do sistema, K UG é o coeficiente de transmissão do gerador controlado (com a dimensão (rad/s)/V), e K F e k F (p) - multiplicadores constantes e dependentes da frequência da função de transferência do filtro K Ф (p) = K Ф k Ф (p). Na ausência de filtro, ou seja, com K Ф (p) = 1,

K BH (p) = K 0 /(1 + rt 0), (3)

onde t 0 = 1/K FD K UG. A função de transferência (3) é uma função de um filtro passa-baixa polinomial de 1ª ordem. Em geral, a ordem do sistema PLL é igual a um mais a ordem do filtro aplicado Ф (circuito integrador ou filtro passa-baixa).

As funções de transferência (2) e (3) são funções “externas” do sistema PLL, condicionadas pelas entradas e saídas do sistema. A principal função do sistema é

K D j (p) = D j /D w em = /, (4)

onde D j é a mudança na diferença de fase na entrada PD, devido à mudança na frequência de controle D w entrada, e 1 + pt 0 /k Ф (p) no denominador da função é o polinômio do sistema (de acordo com a terminologia da teoria da filtragem polinomial), presente em todas as funções de transferência “externas”, inclusive em (2), diferindo em expressões no numerador.

Elementos do sistema PLL

Como já foi dito, os principais elementos (obrigatórios) do sistema PLL são o PD e o PG, que nos sistemas em consideração podem ser analógicos ou pulsados. Além disso, os sistemas PLL considerados podem incluir filtros analógicos, divisores de frequência com saídas de pulso ou analógicas, misturadores, etc.

Detectores de fase. Na Fig. A Tabela 2 mostra as características dos detectores dos PDs mais utilizados:

- característica senoidal de detecção de fase de detectores analógicos de amplitude-fase multiplicadores e comutadores (APD) (Fig. 2a);

- característica dente de serra do pulso de disparo PD (Fig. 2b);

- característica triangular do pulso multiplicador PD (Fig. 2c) (sua versão também é mostrada na Fig. 2d);

- característica dente de serra da detecção de fase de um detector de fase-frequência de pulso de disparo bipolar (PDF) (Fig. 2d).

Arroz. 2

Em primeiro lugar, notamos que as características do detector são estáticas, nas quais o erro dinâmico inerente aos PDs pulsados não aparece. Em PDs analógicos, a diferença de fase instantânea é medida

D j (t) = j 1 (t) - j 0 (t) = d j (t),

onde, no caso mais simples, j 1 (t) = w 0 t + d j (t) e d j (t) são a fase e a mudança de fase modulante do sinal detectado, e j 0 (t) = w 0 t é o fase da oscilação de referência. Ressaltamos que estamos falando da diferença de corrente entre os valores instantâneos j 1 (t) e j 0 (t), contados simultaneamente nos mesmos instantes de tempo t.

Nos PDs pulsados, ao contrário dos analógicos, o intervalo de fase D j (D t i) é medido, proporcional ao intervalo de tempo D t i = t 0i – t i, onde t 0i e t i são momentos diferentes no tempo em que as fases do sinal j 1 (t i) = w 0 t i + d j (t i) e vibração de referência j 0 (t 0i) = w 0 t 0i são iguais. Normalmente são tomados pontos com valores instantâneos zero da senóide (Fig. 3a), que garantem a formação de pulsos PD de entrada e, consequentemente, de saída mostrados na Fig. 3b-d. Se j 1 (t i) e j 0 (t 0i) forem iguais, o intervalo de tempo é D t i = d j (t i)/w 0, e o intervalo de fase é

D d (D t i) = w 0 D t i = d j (t i), (5)

De acordo com (5), os intervalos de fase medidos D j (D t i) são numericamente iguais às diferenças de fase instantâneas desejadas d j (t i). Contudo, deve-se levar em conta que na escala de tempo atual a sequência de leituras intervalares é equivalente à sequência de leituras instantâneas em pontos discretos t j = t i + D t i /2 - em vez dos pontos ti a que correspondem. Como resultado, a fase será medida com um erro de tempo D t i /2:

D j (t i) = d j (t i + D t i /2)

Consideremos as características do detector do PD. As características do NPD analógico multiplicador mostrado na Fig. 2a, é determinado pela expressão

U NPD = K NPD Ucosj, (6)

onde U é a amplitude da tensão detectada, j é a diferença de fase entre as tensões detectada e de referência, e K APD é o coeficiente de detecção dependendo da amplitude da tensão de referência, que portanto deve ser constante. Ambas as tensões, detectadas e de referência, são senoidais. A expressão (6) também é válida para um APD analógico de comutação usando uma chave de tensão senoidal detectável controlada por uma tensão de onda quadrada de referência. No caso geral, um APD analógico, conforme (6), detecta não apenas a diferença de fase, mas também a amplitude da tensão detectada U, por isso é denominado amplitude-fase. De acordo com o acima exposto, durante a detecção de fase, a amplitude não apenas da referência, mas também da tensão detectada deve ser mantida constante. A dependência de u do APD em U é uma desvantagem do detector se ele for usado como detector de fase (um APD comutado também pode ser usado como detector de amplitude síncrona). Outra desvantagem do NPD analógico é a não linearidade de suas características e, portanto, suas seções estreitas são utilizadas para detecção, por exemplo, de p /4 a 3p /4 ou de -3p /4 a -p /4. Ao introduzir uma mudança de fase j 0 = -p /2, o ponto operacional na característica NPD (Fig. 2a) é deslocado para a esquerda pelo ângulo especificado, e o argumento j em (6) é substituído por uma mudança de fase detectada Dj. Como resultado,

U NPD = Para NPD UsinD j = Para NPD UD j, (7)

onde a segunda parte (aproximada) da expressão, proporcional a D j, é para uma seção do intervalo de fase D j de -p /4 a p /4.

Observe que um multiplicador analógico, que apresenta as desvantagens acima (quando usado como detector de fase), é amplamente utilizado como misturador em conversores de frequência, que exigem alta “pureza” do espectro de frequência convertido, e para os quais multiplicadores analógicos são elementos ideais .

Como um pulso multiplicador PD com a característica da Fig. 2c (inversa à característica da Fig. 2a) geralmente utilizam um microcircuito “OU Exclusivo”, mas possui níveis de saída instáveis “0” e “1” e, portanto, é de pouca utilidade para medir diretamente a diferença de fase. Portanto, um multiplexador analógico com entrada de endereço de dois bits é usado como entrada PD. Tal multiplexador pode ser imaginado como consistindo de um microcircuito de detecção de fase “OU Exclusivo” e uma chave de saída controlada por ele. O uso de um comutador e tensões precisas comutadas garante a obtenção de características PD precisas. Além disso, dependendo da escolha dos níveis de tensão comutados, é possível alterar o valor do coeficiente de conversão (detecção), bem como deslocar verticalmente a característica e sua inversão. Na Fig. A Figura 2d mostra a característica deslocada devido às tensões comutadas -E e E (em vez de 0 e 2E, que correspondem à característica da Fig. 2c). Além disso, a característica da Fig. 2d é mostrado como uma função de D j para j 0 = p /2 (semelhante a (7) para APD):

U FD = K FD D j, (8)

A característica (8) é linear na faixa de operação de -p /2 a p /2.

Os PDs de pulso multiplicador são amplamente utilizados em sistemas PLL. Observemos as seguintes características na operação de PDs: em PDs pulsados, os níveis constantes de fontes “estranhas” são comutados, enquanto em NPDs analógicos comutados a tensão detectada é comutada. E, além disso, nos PDs pulsados a chave é controlada por pulsos da saída do multiplicador, enquanto nos APDs analógicos a chave é controlada pela tensão de referência.

A característica de um pulso de disparo PD, por exemplo, do tipo gatilho RS (Fig. 2b), difere das características consideradas na faixa de fase duas vezes maior - de 0 a 2p e a inclinação da seção de trabalho da característica de apenas um sinal - positivo ou negativo (a inclinação positiva da característica mostrada na Fig. 2b pode ser alterada para negativa “invertendo a polaridade” das entradas ou saídas do trigger). Para aumentar a precisão da característica, como “OR Exclusivo”, um comutador com tensões precisas chaveadas pode ser ligado na saída do gatilho. É significativo que o FD em consideração seja um gatilho e opere “na frente”, enquanto os FD multiplicadores operem “na duração”. Por esse motivo, o gatilho (trigger) PD possui menor imunidade a ruídos e, além disso, seu uso leva a processos transitórios no início das mensagens demoduladas. A característica de fase do PPD é uma combinação de duas características do pulso de disparo PD, somadas com sinais opostos (Fig. 2e). Nos PFDs modernos, amplamente utilizados em sintetizadores de frequência, foram tomadas medidas para garantir a “casamento” de alta qualidade de duas características, nas quais praticamente não há ruído de detecção (os chamados PFDs de baixo ruído). A faixa de fase do PFD é de -2p a 2p. A polaridade dos pulsos de saída PPD é determinada pelo sinal, e a duração, como em um gatilho convencional PD, é determinada pelo valor da diferença de fase medida (intervalo de fase). Normalmente, os PFDs possuem uma saída de corrente (com alta resistência de saída), o que se mostra conveniente na construção de sistemas com circuitos integradores proporcionais passivos como filtro. No modo estacionário, ao utilizar um sistema PLL com astatismo de fase, a duração dos pulsos na saída PFD é zero (não há pulsos). Este modo é o principal ao usar PFD em sintetizadores de frequência. Quando há uma incompatibilidade de frequência, o PFD opera como um detector de frequência com uma característica de detecção de relé bipolar que depende do sinal da incompatibilidade.

Arroz. 3

As características dos PDs de todos os tipos são periódicas, o que se deve à periodicidade das mudanças no ângulo de fase. As inclinações positivas ou negativas das características PD do pulso analógico ou multiplicador determinam o sinal positivo ou negativo da função de transferência PD, que é selecionada automaticamente pelo PLL quando ele é ligado. Ao mesmo tempo, o sistema fornece feedback negativo levando em consideração os sinais (mais ou menos) dos coeficientes de transmissão de outros elementos. Ao contrário das características sinusoidais ou triangulares do PD, as características dente de serra do gatilho PD e PPD requerem uma seleção preliminar do sinal da inclinação, que, como mencionado acima, pode ser alterado “invertendo a polaridade”.

Normalmente, um PD, assim como um detector de qualquer tipo, é entendido como um elemento composto por duas partes - detecção e filtragem. Na construção de um sistema PLL, sua primeira parte detectora é utilizada como PD, e o filtro aplicado é considerado um elemento do sistema. O sinal de saída PD contém um componente útil, proporcional ou quase proporcional (dependendo do tipo de PD) à diferença de fase detectada, bem como componentes de alta frequência que aparecem na forma de ondulações e geralmente estão sujeitos a filtragem. O espectro de ondulação é determinado por uma portadora com duplicação de frequência (para multiplicação de PDs e comutação de PDs com duplicação) ou sem duplicação de frequência (para comutação de PDs sem duplicação e acionamento de PDs).

Além do acima exposto, notamos que os sinais de entrada dos PDs analógicos e de pulso multiplicador devem ser senoidais ou retangulares, respectivamente, com ciclo de trabalho de 2. Para PDs de disparo, o cumprimento do ciclo de trabalho não é necessário, mas deve ser levado em consideração que a diferença de fase entre as bordas do pulso que disparam e disparam o reset.

Geradores controláveis. Como já mencionado, o OG no sistema PLL pode ser analógico ou pulsado (como o PD). Um oscilador analógico pode ser um gerador de transistor de banda estreita de alta frequência (centenas de MHz, unidades de GHz) com um circuito oscilante, que usa varicaps controlados por tensão (varatores). O gerador não requer a polarização E0 mostrada na Fig. 1a,b. Seu modo é fornecido por seu próprio circuito de polarização. A tensão de saída do gerador é senoidal, mas ao usar um comparador pode ser de onda quadrada (pulso).

Um conversor tensão-frequência de banda larga com integração contínua e balanceamento de carga, também conhecido como modulador PFM, pode ser usado como UG pulsado (com frequência de até vários MHz). A frequência de tal UG (seus valores discretos instantâneos) é proporcional à tensão analógica convertida (seus valores instantâneos nos mesmos pontos de referência de tempo). Um exemplo do UG em consideração poderiam ser os conversores AD650 e AD654 da Analog Devices. Existe um tipo de UG com sincronização da frequência do sinal de saída por pulsos de clock (AD652, AD7741/2). Este tipo de gerador é semelhante a um modulador sigma-delta e destina-se ao uso em sistemas com conversão digital.

Arroz. 4

Na Fig. A Figura 4a mostra um diagrama de blocos de um UG pulsado (sem sincronização), e a Fig. 4b - diagramas de tensões em seus elementos. Também mostra as tensões nos elementos de um sistema PLL sem filtro com o UG pulsado considerado e PD pulsado multiplicador. Na Fig. 4a,b: Uin - tensão na entrada de controle do PD; U arr é a tensão de realimentação na outra entrada do PD, que é a tensão de saída do UG (U UG); U vxUG - tensão de entrada do UG, que é a tensão de saída do FD (U FD); U int, U comp e U single são as tensões do integrador, comparador e monovibrador como parte da unidade de controle. Os diagramas de tensão ilustram claramente o processo de operação do VG e do sistema PLL como um todo. Verifica-se, em particular, que UvxUG é “filtrado” no integrador: o resultado da integração, completado pelo funcionamento do comparador, é determinado pela área de tensão integrada U inxUG e não depende da sua forma.

Divisores de frequência. Os divisores de frequência, incluídos no circuito de feedback entre a unidade de controle e o PD, garantem a multiplicação da frequência pelo sistema PLL na saída da unidade de controle. Contadores convencionais ou divisores especialmente criados para sintetizadores de frequência (em combinação com contadores conectados na entrada do sistema PLL) podem ser usados como divisores. Os sintetizadores de frequência fornecem multiplicação de frequência fracionária com alta resolução, implementada por meio de ajuste de software. Divisores de frequência especiais usados em sintetizadores incluem divisores dos tipos “N inteiro” e “N fracionário” (com coeficientes de divisão inteiros e fracionários, respectivamente). Os primeiros são amplamente utilizados em sintetizadores de frequência, os segundos são novos, proporcionando parâmetros mais elevados para sintetizadores. Os sintetizadores digitais (DDS) com saída analógica mencionados acima também podem ser usados como divisores de frequência.

Normalmente, os dispositivos que usam um sistema PLL são produzidos como microcircuitos em um único chip. Os filtros externos são os discutidos a seguir, bem como os circuitos de ajuste de frequência de geradores controlados contendo elementos indutivos, capacitores e varicaps (varatores).

Modo de operação PLL

Arroz. 5

Na Fig. A Figura 5a mostra um diagrama do sistema PLL (de forma simplificada sem filtro) com a designação das grandezas que caracterizam o modo de operação do sistema (para um amplificador, tal modo seria denominado modo DC). Na Fig. 5a, a variável de controle é a frequência w0 na entrada, que, graças ao loop de bloqueio de fase, é igual à frequência do UG, e a tensão de controle do UG e, consequentemente, a tensão de saída do FD são iguais para E 0 = C 0 /K UG. A diferença de fase inicial na entrada PD com a característica da Fig. 2c (multiplicando o pulso PD com tensões chaveadas 0 e 2E) é igual a j 0 = E 0 /K PD = = w 0 /K PD K UG = w 0 t 0 . Normalmente j 0 = p /2 ou -p /2 é selecionado, no qual o ponto de operação está no meio da seção linear da característica.

Na Fig. A Figura 5b mostra uma versão do circuito com uma fonte de polarização externa E0, correspondente ao circuito da Fig. século 1 Nesta modalidade, a tensão na saída PD é zero, mas a fase inicial, como no caso anterior, é j 0 = p /2 ou -p /2. Este último é garantido por tensões de comutação PD iguais a -E e E, e corresponde à característica da Fig. 2g. Na realidade, nos diagramas da Fig. 5a,b, a diferença de fase inicial e a tensão de saída do PD terão pequenos desvios dos valores especificados, o que se deve ao autoajuste do sistema para compensar a influência dos desvios dos parâmetros PD e HC e do tensão E0 da fonte externa dos valores nominais especificados.

Apesar da complexidade, o diagrama da Fig. 5b (Fig. 1c) pode ser mais preferível pela seguinte razão. O fato é que a constante de tempo t 0 determina, junto com k Ф (p), as propriedades dinâmicas do sistema e, portanto, deve ser possível selecionar o valor desejado. Ao mesmo tempo, para o circuito da Fig. 5a, de acordo com a expressão acima para j 0, as quantidades t 0 e j 0 estão inter-relacionadas, e uma mudança em t 0 implicará uma mudança em j 0. Como resultado, o modo especificado do PD e do sistema PLL como um todo mudará. Esquema na Fig. 5b está livre desta desvantagem e t 0 pode ser selecionado independentemente de j 0.

Propriedades de frequência do sistema PLL

A função de transferência (3) é uma função de 1ª ordem. Aplicar um filtro ao PLL altera as propriedades dinâmicas do sistema. O polinômio do sistema (o polinômio no denominador das funções de transferência) determina a ordem, tipo de aproximação e faixa de frequência da filtragem, e o termo ou polinômio no numerador determina o tipo de filtragem (passa-baixa, passa-alta , ou filtragem passa-banda) e o coeficiente de transferência.

Arroz. 6

Os sistemas PLL de 2ª ordem normalmente usam um dos filtros de 1ª ordem mostrados na Fig. 6 (observe que o nome geralmente aceito “filtro” neste caso é condicional; seria mais correto considerá-los circuitos de correção de frequência):

- filtro integrador (IF) (Fig. 6a) com função de transferência K Ф (p) = U saída /U entrada = 1/(1+p t Ф) = k Ф (p) em K Ф = 1, onde t Ф = RC - constante de tempo do filtro;

- filtros integradores proporcionais (PIF) (Fig. 6b, c) com função de transferência K Ф (p) = saída U / entrada U = = (1 + p t Ф1)/(1 + p t Ф) = k Ф (p) em K Ф = 1, onde t Ф = RC, t Ф1 = R2C, R = R1 + R2;

- circuitos de integração proporcional (PI) (Fig. 6d, e) com função de transferência K Ф (p) = U out / I input = K Ф k Ф (p), onde K Ф = R, k Ф (p) = 1 + 1/p t Ф1 , t Ф1 = RC.

O circuito PI difere do IF e do PIF porque a fonte de seu sinal de entrada é uma fonte de corrente Iin com uma resistência infinitamente grande. Num sistema PLL, o circuito PI é implementado, por exemplo, usando um amplificador operacional PI como um circuito de realimentação negativa paralelo. A função de transferência do circuito com o amplificador é igual a K Ф (p) = -(K Ф + 1/p t Ф) = -K Ф k Ф (p), onde K Ф = R/r, t Ф = rC , r é a resistência de ajuste de corrente do circuito , ligado na entrada do amplificador, e k Ф (p) - de acordo com o PI na Fig. 6d,d. O sinal negativo, determinado pela conexão inversora do amplificador, deve ser levado em consideração no faseamento do PD, caso o PD possua característica dente de serra. Observe que tФ é a constante de tempo “física” do circuito PI, assim como o PIF, enquanto t Ф1 é uma constante de tempo condicional, conveniente para escrever expressões matemáticas. A função de transferência do PI, determinada por K Ф + 1/p t Ф, ao contrário do PIF, consiste em duas funções - proporcional KФ e integradora 1/p t Ф afeta o fator de qualidade e, consequentemente, a estabilidade de. o sistema (em KФ --> 0 o sistema PLL é instável), e o termo 1/p t Ф determina a propriedade integradora do PI, que garante o astatismo do sistema PLL em relação à fase. EM ultimamente Em vez de um amplificador operacional que fornece “fonte de alimentação” de corrente ao PI, é usado um driver de corrente, que é usado em conjunto com o PFD discutido acima. O driver especificado fornece conexão do PI com sua saída “inferior” ao “terra”. Observe que, juntamente com o circuito RC mais simples da Fig. 6d, circuitos de configuração complexa e, consequentemente, ordens superiores são usados como PIs.

Além das saídas principais dos filtros U out, conectadas no sistema PLL à entrada do UG, na Fig. 6b-d mostra as saídas adicionais U out*, que, juntamente com as principais, podem ser utilizadas para captar o sinal de saída do sistema PLL. O uso de saídas adicionais equivale a conectar filtros externos na saída do sistema que não estão envolvidos em um circuito fechado de realimentação. As funções de transferência dos filtros para saídas adicionais, juntamente com as funções para as saídas principais, são fornecidas na tabela.

O polinômio das funções de transferência de um sistema PLL de 2ª ordem, bem como filtros polinomiais da mesma ordem, é determinado pela expressão generalizada 1 + p /w 0 Q + p 2 /w 0 2, onde w 0 é o natural frequência do sistema, conhecida na teoria dos filtros como pólos de frequência, e Q é o fator de qualidade, que determina o tipo de aproximação das características de frequência (de acordo com Butterworth, Chebyshev, etc.). A tabela mostra os polinômios das funções do sistema PLL com diferentes filtros, bem como as expressões correspondentes Q e w 0. A tabela também mostra os dados da função principal K D j (p) (4) e da função de transferência do sistema quando utilizado como demodulador de frequência: K BH ^(p) - com saída após o PD (antes do filtro), K BH (p) - após o filtro e KChD*(p) - ao captar um sinal da saída adicional do filtro. Ressaltamos que o operador p nas funções de transferência do sistema PLL é determinado pela expressão jW, onde W é a frequência de variação da frequência na entrada e, consequentemente, a tensão de saída (para modulação em frequência, esta é a modulação freqüência).

Analisando os dados apresentados na tabela, podem-se tirar as seguintes conclusões. A função K D j (p) de um sistema PLL de 1ª ordem é uma função de filtro passa-baixa, e com PI é uma função PF (filtragem passa-banda) com frequência de ressonância w 0 . A função PF de um sistema com PI determina o astatismo do sistema em relação à fase: o coeficiente de transmissão na frequência zero é zero. A função de transferência K D j (p) de um sistema com IF e PIF é a função total do LPF e PF, que pode ser considerada como uma função do LPF, alterada na região da frequência de corte. Lembre-se de que a filtragem de 2ª ordem é uma filtragem passa-baixa se o numerador da função for um termo de ordem zero (t 0) e uma filtragem passa-banda se for de primeira ordem (pt 0 t Ф1).

As funções K BH (p) e K BH* (p) para um sistema com PIF são idênticas às funções para um sistema com PI, mas são alcançadas nos diferentes K D j (p) indicados acima. A utilização de saídas adicionais, caracterizadas por K BH* (p), garante, ao contrário de K BH (p), a obtenção de funções de transferência como filtro passa-baixa (Fig. 6b,d) e PF (Fig. 6c,e ), e K BH* ( p) do tipo filtro passa-baixa é semelhante ao KChD(p) de um sistema com FI. Uma característica do uso do PIF, comparado ao IF, é que o fator de qualidade requerido pode ser definido alterando a relação R2/R (t Ф1 /t 0) sem alterar t 0 e t Ф e, consequentemente, sem alterar w 0 .

Aplicação do sistema PLL

A utilização de um sistema PLL depende de qual de seus elementos é a entrada e qual é a saída. Vejamos as principais aplicações do sistema PLL.

Demodulador de frequência. Ao usar um sistema PLL como demodulador de frequência, o sinal FM é alimentado na entrada PD (Fig. 1a, c), e o sinal demodulado é removido, por exemplo, da saída do filtro. A função de transferência do demodulador será determinada pelas expressões de numerador e denominador fornecidas na tabela, bem como pela expressão (2). Para filtrar o sinal demodulado com os parâmetros necessários, geralmente é usado um filtro externo adicional. Neste caso, o sistema PLL deve ser considerado como o primeiro estágio de filtragem e levado em consideração no cálculo da função geral de transferência do filtro (com a ordem, aproximação e frequência de corte exigidas).

Modulador de frequência. Ao utilizar um sistema PLL como modulador de frequência, o sinal modulante uin(t) é fornecido à entrada do CG, conforme mostrado na Fig. 1b, e o modulado é retirado da saída do UG. Neste caso, o próprio modulador é o UG, e o sistema PLL define a frequência portadora, determinada pela frequência de referência (controle) na entrada PD. Além disso, o sistema fornece filtragem do sinal modulado, determinado pelos parâmetros selecionados da função de transferência. Em geral, a função de transferência do sistema PLL no modo FM, ao contrário de (2) para demodulação,

K FM (p) = D w fora /u dentro = ,

onde K 0 = t 0 K UG. Ao usar fundos mútuos

K FM (p) = (pK 0 + p 2 K 0 t f)/(1 + pt 0 + p 2 t 0 t f); (9)

K FM *(p) = pK 0 /(1 + pt 0 + p 2 t 0 t f), (10)

Assim, para remover o sinal FM das saídas principal e adicional do PIF (Fig. 6b). A função (9) é a função total do PF e do filtro passa-alta, e a função (10) é a função do PF. A segunda opção de captação de sinal é mais preferível para sinais modulados em banda estreita.

Arroz. 7

Filtros de frequência. Na Fig. A Figura 7a mostra um diagrama de um sistema PLL com filtragem de frequência da tensão uin, e na Fig. 7b - com filtragem de frequência da mudança de frequência modulante Dwin como parte do sinal FM. Ambos os filtros têm a mesma função de transferência

K f (p) = 1/,

que é função do filtro passa-baixa ao usar o IF e a função total do filtro passa-baixa e do PF ao usar o PIF e PI. Além disso, o primeiro dos filtros (Fig. 7a) pode ser usado para captar um sinal das saídas adicionais PIF e PI, para as quais são implementados o filtro passa-baixa e as funções PF, respectivamente.

Deslocador de fase. Acima é mostrada a dependência da diferença de fase constante na entrada PD no modo de operação do sistema PLL (Fig. 5a, b). De acordo com isso, ao captar um sinal da saída do UG, conforme mostrado na Fig. 7b, é possível obter um deslocamento de fase do sinal de saída, por exemplo, j 0 = p /2 ou -p /2 (deslocamento de fase em quadratura). O ângulo j 0 = p /2 é garantido ao escolher a característica PD na Fig. 2d, e j 0 = -p /2 - durante a “inversão de polaridade”, por exemplo, das fontes E e -E. Outros valores de ângulo também são possíveis.

Multiplicador de frequência. A multiplicação de frequência pelo sistema PLL é garantida pela inclusão de um divisor de frequência “:N” no circuito de realimentação, conforme mostrado na Fig. século 7 A frequência na saída do UG, que é a saída do multiplicador, é igual a w out = w 0 N, onde N é o coeficiente de divisão do divisor. Nos sintetizadores de frequência, um divisor de frequência “:R” é incluído adicionalmente na entrada do sistema PLL (não mostrado na Fig. 7c). Como resultado, w 0 = w in /R, e w out = w in N/R, onde R é o coeficiente de divisão do divisor “:R”. O uso combinado de divisores “:R” e “:N” (com coeficientes de divisão programáveis) fornece síntese de frequência em uma ampla faixa e com alta resolução.

A introdução de um divisor de frequência no circuito de realimentação aumenta a inércia do sistema PLL: t 0 = N/K FD K F K UG. A inércia pode ser reduzida introduzindo ganho adicional, que compensará a influência do N, mas existe outra maneira. Os sintetizadores de frequência utilizam, conforme indicado acima, divisores de frequência do tipo “Integer-N” ou “Fractional-N”. Este último, diferentemente do primeiro, é caracterizado por números fracionários do coeficiente N. Portanto, os valores de N para “N fracionário” podem ser menores (por exemplo, N = 10,25 em vez de 1025 para “N inteiro” ) com um valor correspondentemente maior (ao mesmo tempo 100 vezes) w 0 . Com um valor menor de N haverá menos influência em t 0 , e com um valor correspondentemente maior de w 0 as condições para filtrar o sinal PD que chega à entrada do UG são facilitadas.

A multiplicação de frequência também pode ser implementada em um PLL com um sintetizador DDS como divisor de frequência, mas em frequências mais baixas. Se para o sintetizador ADF4113 (com “Integer-N”) as frequências sintetizadas são de até 3,7 GHz, então para o multiplicador de frequência com o sintetizador AD9852 DDS é de até 300 MHz. A multiplicação de frequência às vezes é combinada com modulação de frequência (manipulação), como, por exemplo, no chip transceptor AD6411. Observe que ao multiplicar a frequência de um sinal FM, não apenas a frequência da onda portadora é multiplicada, mas também o desvio de frequência.

Arroz. 8

Conversão de frequência com loop de bloqueio de fase. Na Fig. A Figura 8a mostra um diagrama de um sistema PLL com um conversor de frequência embutido contendo um mixer “X” e um filtro passa-banda PF sintonizado para a diferença de frequência w 0 = w 1 – w 2 (chip AD6411). A quantidade de entrada é w 1 + D w in com a portadora w 1, e a saída é a tensão u out. O dispositivo em questão é um demodulador de frequência, no qual a desmodulação é precedida pela conversão de frequência. Uma característica especial do dispositivo, ao contrário da inclusão usual de conversor e demodulador (sem feedback), é que ele ajusta automaticamente o sistema para a diferença de frequência w 0. É definido como valor de controle na entrada PD.

O dispositivo em questão pode ser utilizado não só para demodulação, mas também para conversão de frequência, sem captar o sinal de demodulação. Neste caso, a portadora convertida é w 2, e o sinal é retirado da saída do UG, conforme mostrado na Fig. 8b. A função de transferência do demodulador da Fig. 8a

K BH (p) = K 0 /, (11)

onde k Ф (p) e k PF (p) são multiplicadores variáveis das funções de transferência Ф e PF, e K 0 = 1/K УГ. No caso mais simples, se o PF for de segunda ordem com k PF (p) = ap/(1 + ap + bp 2),

K BH (p) = K 0 /

é uma função de filtro passa-baixa, cuja ordem é reduzida em um devido ao multiplicador ap no numerador da função PF. A expressão para a função de transferência do conversor é a mesma do demodulador, mas com K0 = 1.

Modulação em quadratura com loop de bloqueio de fase. Na Fig. A Figura 8c mostra um diagrama de um modulador de quadratura baseado em um sistema PLL utilizado em sistemas de radiocomunicação GSM e DCS (chip AD6523). O loop do sistema PLL apresenta um modulador de quadratura “Mod.”, em cuja entrada está um conversor de frequência “X”. A função de transferência do modulador na Fig. 8v

K mod (p) = D w fora /u dentro = K mod /, (12)

onde K mod = D w mod /u input é o coeficiente de transmissão do modulador “Mod.”. Se houver filtragem passa-banda no sistema, ela é adicionalmente levada em consideração em (12) semelhante a (11).

Observemos o seguinte fato interessante. Nos sistemas da Fig. 8, são utilizados misturadores e um modulador, que são multiplicadores de sinal e, portanto, são elementos não lineares (como, de fato, um detector de fase). Mas para as frequências e fases dos mesmos sinais, eles são somadores ou subtratores. Como resultado, para alterar a frequência, o mixer e o modulador são elementos lineares.

A utilização do sistema PLL não se limita aos exemplos dados. Qualquer sistema cuja operação seja baseada em loop de bloqueio de fase é, portanto, um sistema PLL de uma forma ou de outra. Os componentes listados acima dos fabricantes são exemplos típicos do uso de um sistema PLL. Os componentes que utilizam o sistema PLL distinguem-se pela sua variedade e elevadas características técnicas.

Literatura

- Sistemas de sincronização de fases com elementos amostrais / Ed. V.V. Shahgildyan. - M.: Rádio e comunicações. - 1989.

- Fomin A.A. e outros. Medidores e demoduladores de fase síncrona analógicos e digitais. - M.: Rádio e comunicações. - 1987.

- Levin V.A. e outros. Sintetizadores de frequência com sistema de bloqueio de fase de pulso. - M.: Rádio e comunicações. - 1989.

- Curtin M., O'Brien P. Loops de fase bloqueada para receptores e transmissores de alta frequência // Analog Dialogue, Analog Devices, 1999, Vol. 33, não. 3, 5, 7.

- Fague D. OthelloTM: Um novo conjunto de chips de rádio de conversão direta elimina estágios IF // Analog Dialogue, Analog Devices, 1999, Vol. 33, não. 10.

- Transceptor Golub V. GJRF10 da Gran Jansen AS // Chip News. - 1998. - Nº 4. - P. 30–32.

- Moschitz G., Horn P. Projeto de filtros ativos. - M.: Mir. - 1984.

- Golub V.S. Frequência instantânea e média de oscilações e integração de moduladores FM e PFM // Engenharia de rádio. - 1982. - vol. 37. - Nº 9. - P. 48–50.

- Golub V. Uma olhada no ADC sigma-delta // Chip News. - 1999. - Nº 5. - P. 23–27 (conforme alterado no Nº 8, p. 48).

- Resumo técnico SWRA029: Noções básicas de PLL fracionário/inteiro-N / C.Barrett. - Texas Instruments, agosto de 1999.

- Golub V.S. Circuito equivalente do sistema PLL // Izv. universidades Radioeletrônica. - 1994. - vol. 37. - Nº 8. - P. 54–58.

Uma pesquisa na Internet por um dispositivo que corresponda ao título deste artigo não teve êxito. Nos Fóruns eles acreditam que tal dispositivo não pode ser criado. Porém, atualmente, um protótipo de ADC de 16 bits foi fabricado e testado no microcontrolador ATmega 16 (MCU), que faz parte de um produto comercial.

Descrição do esquema

A Figura 1 mostra um diagrama esquemático do ADC desenhado no programa Proteus 7.7. A programação do MK foi realizada no IAR Embedded Workbench utilizando o “Curso de Treinamento” autor: Pashgan no site O funcionamento do ADC foi verificado no hardware. A simulação da operação do ADC no Proteus falhou, o motivo é descrito abaixo.

Figura 1 Diagrama esquemático de um ADC de 16 bits.

Uma descrição detalhada de todos os elementos (chips) do circuito pode ser encontrada na Internet, vamos considerar a finalidade de cada elemento do circuito ADC;

Microcontrolador ATmega 16

O diagrama do sinal MK é mostrado na Figura 2. O MK deve gerar 2 sinais de clock de frequência fixa de 122 Hz (16 MHz/65536 = ~122 Hz). O contador-temporizador MK T1 opera em “modo normal”, sem prescaler, com comutação de estado das saídas OC1A e OC1B, e gera pulsos retangulares do tipo “meandro” nos pinos 18 e 19, que são deslocados em 90°. Para fazer isso, um número igual à metade do valor máximo do código do temporizador T1 é gravado no registro de comparação OCR1B. Na saída do chip D4B (elemento lógico OR exclusivo), são gerados pulsos retangulares F1 de dupla frequência (244 Hz), que são fornecidos à primeira entrada (pino 14) do Detector de Fase (PD) do Phase Locked Loop (PLL) chip D2. A borda anterior dos pulsos F1 sempre coincide com o código zero do temporizador T1. Em um circuito real, devido a atrasos nos elementos do circuito, o deslocamento inicial do código zero não excede 5 unidades do bit menos significativo (EMB) do temporizador T1 e deve ser levado em consideração na geração do resultado da conversão ADC. No layout ADC, o atraso no MK é de 2 EMP (0,125 μs) em 2 elementos D4 – 3 EMP (0,15 μs)

Arroz. 2. Diagrama de sinais do MK e dos microcircuitos D2 e D4.

Se o ATmtga 16 MCU estiver configurado para o modo de “captura” do estado do contador-temporizador T1 (“captura”), e pulsos retangulares com frequência de 244 Hz forem fornecidos à entrada de “captura” ICP1, cuja borda principal ficará atrasado em fase atrás da borda principal dos pulsos F1, então o código de mudança de fase de 16 bits entre as bordas iniciais dos pulsos F1 e F0 será lido no registro ICR1 de 16 bits. A escolha dos símbolos para os sinais F1 e F0 está associada à lógica de funcionamento do microcircuito PD pulsado D2 74HC4046. A borda inicial do pulso F1 define a saída PD (pino Tx 15 D2) para o estado “Log.1” e a borda inicial do pulso F0 para o estado “Log.0”. No Proteus, o símbolo do pino 15 do chip D2 “ZENER” difere da designação “PHASE COMPARATOR III”, que é fornecida no manual de utilização do chip. No diagrama da Figura 1, esse erro permanece, pois Falha ao corrigir os gráficos do item de biblioteca 74HC4046.

Para resolver o problema: crie um ADC de 16 bits em um AVR de 8 bits, você precisa de um dispositivo que deva converter um sinal analógico (por exemplo, tensão) na duração dos pulsos Tx (mudança de fase entre os pulsos F1 e F0), cuja tensão média é igual à tensão de entrada Ux. Este dispositivo é descrito detalhadamente no artigo “Conversor de tensão para largura de pulso estabilizado por PLL” da revista. Mais adiante na descrição serão utilizados materiais deste artigo, necessários para explicar o princípio de funcionamento do ADC. Para exibir os resultados da conversão ADC, um display LCD alfanumérico TC1602-A, D5 é usado na Figura 1.

Chip 74НС4046 e amplificador operacional ½ pacote D3 (AD823)

O microcircuito 74NS4046 e um amplificador operacional (op-amp) formam um circuito PLL, cuja entrada recebe um sinal de pulso F1. O PLL é um sistema de controle automático com Feedback Negativo (NFB), que ajusta a frequência do Oscilador Controlado por Tensão (VCO) interno para que sua frequência Fo seja igual à frequência do sinal de entrada F1, Figura 3. O ajuste é realizado devido à presença de feedback negativo. O sinal de saída do VCO, pulsos retangulares com frequência F0, é comparado no Detector de Fase (PD) com o sinal de entrada F1, o sinal de erro de fase após filtragem e amplificação é usado para ajustar a frequência de saída do VCO.

Fig.3 Diagrama funcional do PLL.

O circuito PLL é semelhante ao circuito Amplificador Operacional (OPA), com a única diferença de que a variável de entrada é a fase de oscilação e a frequência (taxa de mudança de fase) é o sinal de feedback.

Arroz. 4. Diagrama de blocos PLL.

Devido ao fato de a sintonia ser realizada por diferença de fase, o sistema é asstático em relação à frequência: em estado estacionário, a frequência de sintonia é exatamente igual à frequência do sinal de entrada (Fo=F1), e a mudança de fase é definido de forma que a tensão de saída do filtro passa-baixa (Ugun) garanta igualdade de frequências. Sob certas condições, que dependem do tipo de filtro passa-baixa, o sistema PLL pode ficar asstático e desfasado. Mais descrição detalhada O PLL, com as conclusões das fórmulas, pode ser encontrado na internet e em livros.

O sistema PLL é usado principalmente para modulação e desmodulação de frequência e fase, multiplicação e conversão de frequência, filtragem de frequência ou extração de forma de onda de referência para detecção de sinal coerente. Normalmente, o sinal de entrada em dispositivos PLL é a frequência. Um PLL é um sistema de controle de loop de feedback no qual os parâmetros de controle são a frequência ou fase do sinal, em vez da magnitude de sua tensão ou corrente. O dispositivo proposto usa um circuito de comutação PLL não padrão com um parâmetro adicional de regulação de tensão.

Vamos introduzir no circuito PLL padrão um gerador G do sinal F1 com frequência fixa e um elemento de comparação na entrada do filtro passa-baixa, que deve comparar a tensão de entrada Ux com o sinal de saída do PD. Vamos mudar o design do diagrama funcional PLL. A Figura 5 mostra um diagrama funcional de um conversor de sinal analógico (tensão Ux) em duração de pulso Tx, Modulação de Fase de Pulso (PPM) com PLL.

A modulação de fase (PM) é um dos tipos de modulação de oscilação, onde a fase da oscilação da portadora é controlada por um sinal de informação (mudança periódica na fase de oscilação de acordo com uma determinada lei; lenta em comparação com o período de oscilação). Da definição de PM segue-se que existe um gerador de sinal senoidal no qual a fase do sinal de saída muda ao longo do tempo. Este tipo de modulação é utilizado na engenharia de rádio para transmitir informações. PM é geralmente considerado para sinais senoidais.

Fig.5 Diagrama funcional do conversor do sinal analógico Ux em duração de pulso Tx.

O dispositivo proposto utiliza modulação de fase de sinais de pulso. Se usarmos um PD pulsado com característica de saída linear, obteremos um conversor de precisão de tensão Ux para duração de pulso Tx. Neste conversor, o sinal de entrada analógico Ux é comparado com o sinal de saída Tx (mais precisamente, com o valor médio do pulso Tx durante um período de frequência Fo (área de pulso Tx) com o valor médio de Ux no mesmo tempo) . A presença de OOS e um grande ganho (Ku) do filtro passa-baixa proporcionam alta precisão de conversão e permitem reduzir os requisitos de precisão e estabilidade de todos os elementos do circuito cobertos por OOS. A implementação de hardware do circuito proposto não é uma tarefa difícil; muitos circuitos integrados PLL diferentes são produzidos atualmente, por exemplo, o microcircuito CD4046 (análogos domésticos 1561GG1 e 564GG1) inclui 2 tipos de PDs, um VCO e circuitos de controle VCO adicionais. O microcircuito 74NS4046, análogo funcional do CD4046, possui 3 tipos de PDs e pode operar em frequências mais altas. A Figura 6 mostra a implementação de hardware de um filtro passa-baixa para tensões de entrada negativas.

Fig.6 Circuito de filtro passa-baixa para tensões de entrada negativas.

O filtro passa-baixa é feito de acordo com o circuito de um filtro de integração proporcional em um amplificador operacional (filtro PI), que compara os valores médios dos sinais Ux e Tx ao longo do período de frequência Fo, resistores R1 e R2 determinar o fator de comparação de escala. O produto C1*R1 (constante de tempo do integrador Ti) determina o efeito integrador do filtro, o resistor R3 garante a estabilidade do circuito PIM e a relação de R3 para R1 determina o coeficiente proporcional do filtro Kn. Se o PD tiver uma característica de saída na região de tensões positivas, então o sinal de entrada deverá ter polaridade negativa. Se o sinal de entrada for positivo, então é necessário usar um circuito de comutação diferencial do amplificador operacional, Fig. Os elementos do circuito do filtro passa-baixa devem atender ao seguinte requisito: R3/R1 = R4/R2 e R1*C1 = R2*C2.

Fig.7 Circuito de filtro passa-baixa para tensões de entrada positivas.

O sinal de saída do filtro passa-baixa controla o oscilador (VCO) de modo que as frequências dos sinais Fo e F1 sejam iguais, e a mudança de fase entre eles seja tal que a igualdade seja satisfeita.

Ux/R1 = (Para cima/R2)*Tx/T1, (1)

onde Up é a amplitude do pulso Tx (Up é a tensão de alimentação PD);

T1 = período 1/F1 da frequência em que o PLL opera.

A utilização de um filtro PI torna o sistema PLL asstático em fase, o que significa que se R1=R2, então o valor em estado estacionário da duração relativa dos pulsos de saída do conversor (Tx/T1) é determinado apenas pela razão Ux/ Up e não depende dos parâmetros de outros elementos do circuito.

Ux/Cima = Тх/Т1, (2)

Ux = Acima* Tx/T1. (3)

Na fórmula (3), as grandezas conhecidas são a tensão de alimentação PD (Up = 5v) e o período de frequência PLL T1 = (1/16.000)*65.536 = 4,096 ms (valor exato de frequência F1 = 244,140625 Hz). Para medir a tensão de entrada Ux, é necessário medir a duração do pulso Tx (mudança de fase entre as bordas principais dos pulsos F1 e F0) e substituí-la na fórmula (3).

Metodologia para cálculo de elementos de circuito PLL

O parâmetro inicial é a frequência F1 na qual o ADC com PLL deve operar. Para calcular as características dinâmicas dos sistemas de controle, utiliza-se a frequência circular (frequência angular) ω = 2π*F, em [rad/s], dimensão de fase ⱷ em [rad]. Em estado estacionário, quando as frequências são iguais a F1=F0, a característica de saída do PD (pino 15) do chip D2 é mostrada na Figura 8.

Arroz. 8 Característica de saída PD.

Coeficiente de conversão FD (pino 15 do chip D2) Kfd = Up/2 π [V/rad].

O VCO, que faz parte do chip D2, possui 2 vias (2 entradas, pinos 9 e 12) para controlar a frequência de saída F0:

- controle de tensão através da entrada “VCON” (pino 9), além do pino 11 “R1” é conectado um resistor, cuja seleção está descrita no manual de utilização do chip PLL;

- controle de corrente através da entrada “R2” (pino 12), normalmente esta entrada é utilizada para ajustar a frequência inicial do VCO na ausência de tensão para a entrada “VCON”.

No diagrama da Figura 1, é utilizado o 2º método de controle da frequência do VCO, pois neste caso, é permitida uma grande faixa de tensões de saída do filtro passa-baixa, que é feita no chip do amplificador operacional D3A (AD823). A tensão de saída do amplificador operacional, que pode variar de menos 15 V a +15 V, é convertida pelo resistor R5 na corrente de controle de frequência VCO. Ao selecionar os valores dos elementos do circuito (C2, R4 e R5), o VCO é ajustado de tal forma que na tensão de saída zero do filtro passa-baixa (Ugun = 0 V), a frequência de saída do VCO é Fo = 244 Hz ± 10%, e com Ugun = menos 5 V, a frequência de saída dobrou Fo=488 Hz ±10%. Isso permite que você use de maneira ideal toda a faixa linear da tensão de saída do filtro passa-baixa para compensar todas as características não lineares dos elementos do circuito e manter a alta precisão da conversão ADC.

Arroz. 9 Característica de saída VCO.

Características dinâmicas do PLL

Para usar o PLL corretamente, você precisa conhecer as características estáticas e dinâmicas deste dispositivo. Na Internet você pode encontrar uma saída detalhada da função de transferência PLL para diferentes designs de filtro passa-baixa. A Figura 10 mostra um diagrama de blocos de um modelo linear de um ADC com um PLL em estado estacionário, quando, após ligar a energia, o processo transitório (frequência de busca e travamento F1) terminou F0 = F1. As funções de transferência dos elementos do circuito são apresentadas na forma de operador.

Arroz. 10 Diagrama de blocos de um modelo linear de um ADC com um PLL em estado estacionário.

Vamos utilizar a fórmula pronta para a função de transferência W(p) (descrição matemática do comportamento de um sistema dinâmico) de um PLL, no qual é aplicado um filtro PI. A função de transferência (4) corresponde a um link oscilatório de 2ª ordem:

onde p é uma variável complexa que pode ser substituída por jω para construir a AFC do dispositivo;

ωп = 2π*Fп – frequência angular natural da banda passante do PLL em [rad/s];

Fп – frequência natural da banda passante do PLL em [Hz] (frequência transitória do circuito PLL);

ξ – coeficiente de amortecimento (atenuação do processo transitório) do PLL.

A Figura 11 mostra a resposta de frequência logarítmica do PLL em unidades relativas de frequência natural para diferentes valores do coeficiente de amortecimento ξ. Além disso, são fornecidas expressões que conectam os parâmetros da função de transferência PLL com os parâmetros dos dispositivos incluídos no circuito conversor de sinal analógico para duração de pulso.

onde Kfd é a constante do coeficiente de transmissão FD (V/rad);

Kgun – constante do coeficiente de transmissão do VCO (rad/s*V);

Ti = R1*C1 – constante de tempo do integrador do filtro PI (c);

Кп = R3/R1 – coeficiente proporcional do filtro PI;

Fig. 11 Resposta em frequência logarítmica do link de 2ª ordem.

A resposta de frequência do PLL corresponde a um filtro passa-baixa de 2ª ordem com frequência de corte ωп (rad/s) (frequência de transição) e inclinação (atenuação) de 20 dB por década (6 dB/oitava). Ao projetar um conversor com PLL, é necessário selecionar a largura de banda do dispositivo ωп=2π*Fп e o coeficiente de amortecimento ξ em frequências acima da frequência de corte.

Vamos determinar os parâmetros de projeto de um ADC real com PLL, mostrado na Figura 1.

Vamos anotar os parâmetros dos elementos de um conversor PLL real em expressão literal (ver Fig. 8 e Fig. 9): Kfd = Uр/2π; Kgun = 2πF0/Up; Ti = 1/F0 e F0= F1. Vamos substituir os valores literais dos parâmetros nas fórmulas (5) e (6) e obter fórmulas simples (para avaliação de engenharia) para calcular as características dinâmicas de um conversor com PLL.

ωп = F0 [rad/s], (7)

Fп = F0/2π [Hz], (8)

ξ = Kn/2. (9)

Vamos substituir os valores de um conversor PLL real nas fórmulas (8) e (9), e obter os seguintes valores:

A largura de banda do conversor com PLL Fp = 244Hz/6,28 = 39 Hz;

- coeficiente de amortecimento ξ = 1/2 = 0,5.

Usando as fórmulas (5) e (6), é possível obter as características desejadas do processo transitório de conversão do sinal de entrada alterando os parâmetros dos elementos do circuito e a frequência de conversão F0.

Resultados do teste do layout ADC com ATmega 16

Para verificar a precisão da conversão da tensão de entrada Ux do ADC com PLL, foi utilizado um voltímetro V7-38, que exibe a tensão medida em 5 casas decimais com erro não pior que 0,05% no limite de 2V, com uma resolução de 0,1 mV e não pior que 0,1% no limite de 20 V com uma resolução de 1 mV.

O layout ADC com PLL possui limite de medição de ~ 6,5V (6553,5mV), a tensão medida é exibida no display LCD (D5) em 5 casas decimais com resolução de 0,1mV. A escolha do limite de medição está associada a um número decimal máximo de 65535, que corresponde ao valor máximo do código binário do contador-temporizador T1. A fonte de tensão de referência ADC é a tensão de alimentação do chip D2 (74HC4046), que na placa de ensaio é igual a Up = 5,029V (5.029,0 mV) (medido por V7-38). Para que o código EMP do contador-temporizador T1 seja igual a 0,1 mV, é necessário cumprir a condição (1), a corrente máxima de entrada Uxmax/R1 deve ser balanceada pela corrente do circuito de realimentação Up/R2 (10) .

65536/R1 = 50290/R2, (10)

R1 = R2* (65536/50290),

R1 = 1,303* R2,

R1 = 130,3 kOhm (ver Fig. 1).

O diagrama na Figura 1 mostra um resistor variável RV1 = 1 kOhm, que é conectado em série com R1 = 130 kOhm para ajustar o fator de escala de conversão ADC. A Tabela 1 e a Figura 12 mostram os resultados da medição da tensão de entrada Ux usando um protótipo ADC com PLL e voltímetro V7-38. A tensão Ux [V] foi ajustada a partir de uma fonte de alimentação de laboratório com voltímetro embutido. As 1ª, 2ª e 3ª colunas da Tabela 1 mostram as leituras dos voltímetros sem levar em consideração o sinal (módulo) para simplificar a comparação das leituras de Ux, V7-38 e ADC. Na 5ª está a leitura do display LCD do ADC, e na 4ª está a leitura do ADC, na qual é excluído o erro de 5 EMP associado ao deslocamento inicial do pulso frontal F1 em relação ao código zero do temporizador T1. Nas 6ª e 7ª colunas da Tabela 1, os valores dos erros relativos de medição em [%] do voltímetro da fonte de alimentação em relação ao V7-38 e as leituras do ADC em relação ao V7-38, respectivamente. Nas leituras do display LCD falta uma vírgula após o 4º dígito, que deverá aparecer após a finalização do programa MK.

Tabela 1.

Fig. 12 Representação gráfica dos resultados do teste de um ADC com um PLL.

Em anexo à carta encontra-se um arquivo “Foto ATsPF.xlsx” com fotografias que registram simultaneamente as leituras do B7-38 e do ADC com PLL. O videoclipe sobre o experimento possui grande capacidade de memória e pode ser enviado ao editor caso haja solicitação.

Análise dos resultados dos testes do layout ADC com ATmega 16

Os resultados da verificação do layout do ADC mostram que o desvio das leituras do ADC das leituras do dispositivo de referência V7-38 não excede 0,02%. Isso indica uma alta linearidade na conversão da tensão de entrada em duração do pulso usando um PLL.

A resolução do ADC, ao medir tensões superiores a 2 Volts, é 10 vezes maior que a do voltímetro V7-38 (0,1 mV para o ADC e 1 mV para o voltímetro V7-38).

A estabilidade das leituras do ADC não excede ±EMP, o que indica o baixo nível de ruído intrínseco do método de conversão de tensão em duração de pulso usando um PLL.

Na realidade, no circuito ADC com PLL, são comparados dois sinais de formatos diferentes, uma tensão constante e pulsos retangulares, que podem ser representados como a soma de uma tensão constante Up/2 e uma série infinita de tensões senoidais (trigonométrica de Fourier série), cuja amplitude depende da duração do pulso Tx, e a frequência é um múltiplo da frequência de conversão ADC (F1).

As propriedades de filtragem dos PLLs são descritas detalhadamente na literatura. O PLL é um filtro de rejeição ideal para interferência com frequências múltiplas da frequência em que o ADC opera. Se o sinal de entrada Ux contiver interferência nas frequências F1, 2 F1, 3F1, etc., então elas serão completamente suprimidas, pois a tensão média (integral) dessas senóides durante o período de frequência F1 é zero. A função de transferência (11) de tal filtro é mostrada na Fig.

Fig. 13 Resposta amplitude-frequência do filtro (11).

(11)

(11)

Esta característica única do PLL é explicada pela propriedade integradora do VCO, cuja frequência de saída é determinada pela tensão média durante o período da frequência operacional F1. Portanto, é possível comparar na entrada do filtro passa-baixa dois sinais de formatos diferentes, uma tensão constante Ux com um sinal de pulso Tx, enquanto o ruído na duração do pulso Tx é determinado pela interferência com frequências que não são um múltiplo da frequência operacional do PLL. Considerando que todos os processos internos do MC e do ADC são sincronizados pela frequência do oscilador de quartzo MC, o ruído de pulso criado pela operação do MC não afeta a estabilidade das leituras do ADC. Portanto, o PLL ADC fornece uma resolução de 16 bits binários (5 decimais). A resolução do ADC embutido no gabinete MK é de 10 bits binários (3 decimais), a estabilidade real das leituras é de 8 bits, o que é 2 ordens de magnitude pior que a de um ADC com PLL.

Limitações que existem em ADCs com PLL e como eliminá-las

O PD do chip PLL (74NS4046) no modo Detector de Frequência (FD), quando o VCO está sincronizado (trava de frequência F1=F0), possui uma característica de saída conforme Figura 14.

Fig. 14 Característica de saída do 74NS4046 (pino 15) no modo buraco negro.